# **Digital ASIC Fabrication**

Design Document

sddec24-12 Client & Faculty Advisor: Dr. Henry Duwe

> Mitchell Driscoll Evan Dunn Baoshan Liang Katie Wolf

sddec24-12@iastate.edu sddec24-12.sd.ece.iastate.edu

> Revised: April 30, 2024 Version 1.2

# **Executive Summary**

# Development Standards & Practices Used

- IEEE 1481-2019 IEEE Standard for Integrated Circuit (IC) Open Library Architecture

- IEEE 1364-2005 IEEE Standard for Verilog Hardware Description Language

- ISO/IEC 9899:2018 Information technology Programming languages C

- WISHBONE System-on-Chip (SOC) Interconnection Architecture for Portable IP Cores

# Summary of Requirements

Our chip framework will:

- Support 15-20 large and small projects created by students

- Allow one project to be active at a time, through configuration of the management core

- Provide interconnections between user projects and chip resource's

- Follow the Efabless chip guidelines and project architecture

- Pass RTL simulation, hardening, GL simulation, and MPW pre-check

- Be used by the ISU Chip Fabrication Co-curricular Team

# Applicable Courses from Iowa State University Curriculum

- CPR E 281 Digital Logic

- CPR E 288 Embedded Systems I

- CPR E 381 Computer Organization and Assembly Level Programming

- CPR E 488 Embedded Systems Design

- E E 330 Integrated Electronics

- E E 465 Digital VLSI Design

# New Skills & Knowledge Acquired Not Taught in Courses

- ASIC chip design and development

- Chip fabrication and tape-out process

- Open-source project architecture Efabless, Caravel

- Open-source tools OpenROAD, OpenLANE, KLayout, GTKWave

- Electronic design concepts synthesis, layout, routing, static timing analysis, clock gating

# Table of Contents

| 1 | Introduction                                                      | 7  |

|---|-------------------------------------------------------------------|----|

|   | 1.1 Problem Statement                                             | 7  |

|   | 1.2 Intended Users                                                | 7  |

| 2 | Requirements, Constraints, and Standards                          | 8  |

|   | 2.1 Requirements & Constraints                                    | 8  |

|   | 2.2 Engineering Standards                                         | 9  |

| 3 | Project Plan                                                      | 9  |

|   | 3.1 Project Management/Tracking Procedures                        | 9  |

|   | 3.2 Task Decomposition                                            | 9  |

|   | 3.3 Project Proposed Milestones, Metrics, and Evaluation Criteria | 10 |

|   | 3.4 Project Timeline/Schedule                                     | 11 |

|   | 3.5 Risks And Risk Management/Mitigation                          | 12 |

|   | 3.6 Personnel Effort Requirements                                 | 12 |

|   | 3.7 Other Resource Requirements                                   | 13 |

| 4 | Design                                                            | 13 |

|   | 4.1 Design Context                                                | 13 |

|   | 4.1.1 Broader Context                                             | _  |

|   | 4.1.2 Prior Work/Solutions                                        | 14 |

|   | 4.1.3 Technical Complexity                                        | 14 |

|   | 4.2 Design Exploration                                            | 15 |

|   | 4.2.1 Design Decisions                                            | _  |

|   | 4.2.2 Ideation                                                    | -  |

|   | 4.2.3 Decision-Making and Trade-Off                               |    |

|   | 4.3 Proposed Design                                               | -  |

|   | 4.3.1 Overview                                                    |    |

|   | 4.3.2 Detailed Design and Visual(s)                               |    |

|   | 4.3.3 Functionality                                               |    |

|   | 4.3.4 Areas of Concern and Development                            |    |

|   | 4.4 Technology Considerations                                     |    |

|   | 4.5 Design Analysis                                               |    |

| 5 | Testing                                                           |    |

|   | 5.1 Unit Testing                                                  |    |

|   | 5.2 Interface Testing                                             |    |

|   | 5.3 Integration & System Testing                                  |    |

|   | 5.4 System Testing                                                |    |

|   | 5.5 Regression Testing                                            |    |

|   | 5.6 Acceptance Testing                                            |    |

|   | 5.7 Bring-Up & Physical Testing                                   |    |

|   | 5.8 Results                                                       |    |

| 6 | Implementation                                                    | 23 |

| 7  | Professional Responsibility 24                          |

|----|---------------------------------------------------------|

|    | 7.1 Areas of Responsibility                             |

|    | 7.2 Project Specific Professional Responsibility Areas  |

|    | 7.3 Most Applicable Professional Responsibility Area 25 |

| 8  | Closing Material                                        |

|    | 8.1 Discussion                                          |

|    | 8.2 Conclusion                                          |

|    | 8.3 References                                          |

| 9  | Team27                                                  |

|    | 9.1 Team Members                                        |

|    | 9.2 Skill Sets Covered by the Team                      |

|    | 9.3 Project Management Style Adopted by the team27      |

|    | 9.4 Initial Project Management Roles27                  |

|    | 9.5 Team Contract                                       |

| 10 | Appendix                                                |

|    | 10.1 Simulation Waveforms                               |

# List of Acronyms

- ASIC Application-Specific Integrated Circuit

- DRC Design Rule Checking

- GPIO General-Purpose Input/Output

- IC Integrated Circuit

- IEEE Institute of Electrical and Electronics Engineers

- IO Input/Output

- IRQ Interrupt Request Signal

- LA Logic Analyzer

- LVS Layout Versus Schematic

- MPW Multi-Project Wafer

- NSPE National Society of Professional Engineers

- PDK Product Development Kit

- RTL Register Transfer Level

- SoC System-on-a-chip

- WB Wishbone Bus

# Terms and Definitions

- **Caravel Harness** Provided chip wrapper around our design, containing the User Area and Management Core

- Efabless Open-source fabrication company who will manufacture our design

- GTKwave Open-source waveform viewer for viewing simulation results from VCD files

- KLayout Open-source tool for viewing and editing mask layouts

- Management Core Part of the Caravel Harness that contains the management utilities, including the SoC and logic analyzer probes

- **OpenROAD** Collection of open-source tools based on OpenLANE, configured and provided by Efabless to generate production files from Verilog descriptions

- **SkyWater 130nm** Fabrication process used by Efabless supported by the SkyWater Foundry

- User Area Region inside the Caravel Harness users are allowed to modify

- Verilog Hardware design language specified by IEEE Std 1364-2005

- Wishbone Bus Peripheral bus used by the Management Core to communicate with peripherals in the User Area

# List of Figures

| Figure 1: Project Timeline          | . 11 |

|-------------------------------------|------|

| Figure 2: Caravel Chip Architecture | . 17 |

| Figure 3: Framework Diagram         | 18   |

| Figure 4: Design Schematic          | 19   |

| Figure 5: Hardening Data            | .21  |

| Figure 6: 32-to-1 Decoder           | 31   |

| Figure 7: N-Bit Register            | . 31 |

| Figure 8: Wishbone Control Module   | 31   |

# List of Tables

| Table 1: Effort Requirements             | 13 |

|------------------------------------------|----|

| Table 2: Project Context                 | 14 |

| Table 3: Areas of Responsibility         |    |

| Table 4: Project-Specific Responsibility |    |

# 1 Introduction

#### 1.1 PROBLEM STATEMENT

Undergraduate students rarely get the opportunity to create a custom digital ASIC (Application Specific Integrated Circuit) and gain experience with chip fabrication. Our project aims to build and silicon-prove a chip framework that will support a continuous cycle of chip designs, or "tape outs," ready for fabrication. The project aims to give interested students experience in chip design and fabrication. The framework we design will provide space for multiple small projects and the ability to run each independently. The project modules will be created by a co-curricular team of students ranging from freshmen to seniors. By breaking the design process into smaller, less complex subprojects, students can complete modules within a semester. Each module will be fabricated and synthesized as a complex macro that can be used in our framework.

#### **1.2** INTENDED USERS

The Iowa State University Chip Fabrication Co-Curricular Team members will be our project's main users. This team will consist of undergraduate students, graduate students, and Electrical and Computer Engineering professors. Additionally, the open-source community will have access to our design through Efabless.

#### **Future Students**

Undergraduate students in the Chip Fabrication team, ranging from freshmen to seniors, will work on their own ASIC projects to gain chip design experience outside their classes. To make the design process more accessible and hands-on, they will need a functional, easy-to-use framework to interface with the built environment and produce their final designs, which are then printed to silicon. The fabricated chip projects can then be leveraged to qualify for extracurricular projects, internships, and career opportunities.

#### **Professors and Educators**

The professors on the Chip Fabrication team will specialize in ASIC fabrication and lead all the team members. They will need to provide hands-on experience for the ISU Chip Fabrication Co-curricular team because they want to help undergraduate students gain chip fabrication experience outside of class. They help direct the efforts of students in that they know the pitfalls and can keep a clear goal in mind. The key is a mix of hands-on guidance while letting the teams conduct their affairs.

#### **Efabless Open-Source Community**

Our project will be submitted to a public, open-source Efabless repository. Our project will be available to Efabless community members to reference in their own designs. The Efabless community will be interested in open-source ASIC development, and members will be looking for project resources, reference, and collaboration.

# 2 Requirements, Constraints, and Standards

#### 2.1 REQUIREMENTS & CONSTRAINTS

#### **Functional Requirements**

Our project client has outlined the following functional requirements our project must fulfill:

- Framework holds 15-20 projects, including small and large projects

- Management wrapper controls which project is active

- One project is active at a time

- Chip resources will be multiplexed between all the projects

- Projects will interface with the Wishbone bus, LA pins, and IO pins

- Framework will include external OpenRAM modules

- Design successfully passes Efabless precheck

#### **Technical Requirements**

To meet the expected functionality, our design implementation must meet the following requirements:

- Development follows the Efabless process

- Design is implemented in Verilog

- Test code is written in Verilog and C

- Final design generates a GDS<sub>2</sub> file

- Design achieves frequency of 20 MHz

#### **User-Based Requirements**

To ensure proper user interaction and bring-up, our project must meet the following requirements:

- The project is fully documented on the ISU Chip Fabrication website

- Detailed descriptions of the project explain the framework architecture

- The framework is straightforward to use with minimal help or troubleshooting

#### **Design Constraints**

In addition to the requirements listed above, our project must comply with the eFabless project constraints:

- The project must use the required directory structure specified in the Caravel documentation

- Hardened project wrapper must have an area of 2.920mm x 3.520mm

- The top module must be named "user\_project\_wrapper"

- Pin placement and pin sizes must match the golden user\_project\_wrapper in the Caravel repository

#### 2.2 Engineering Standards

- IEEE 1481-2019 IEEE Standard for Integrated Circuit (IC) Open Library Architecture

We are creating an ASIC that should meet timing and power constraints.

- IEEE 1364-2005 IEEE Standard for Verilog Hardware Description Language

All of our modules, as well as the project wrapper, will be implemented in Verilog.

- ISO/IEC 9899:2018 Information technology Programming languages C

Our test programs for the management core will be written in C.

- WISHBONE System-on-Chip (SoC) Interconnection Architecture for Portable IP Cores

- The Wishbone Bus is an open-source hardware bus used for communication between different parts of an integrated circuit. Our design will use this bus to interface between the management core and user projects.

# 3 Project Plan

#### 3.1 PROJECT MANAGEMENT/TRACKING PROCEDURES

Our team will use a combination of agile and waterfall methodologies for project management. This allows for structured planning with clear expectations and milestones while offering flexibility. Since our project has set goals that are required before we can move on to later steps, as well as a hard deadline goal, using waterfall allows us to clearly outline a timeline to follow. We will utilize agile to adapt to unforeseen complexity or challenges as issues arise. We will meet weekly, where we can adapt our team's focus if needed.

We will track our progress through communication on Microsoft Teams and shared files on Google Drive. We will also utilize GitLab for version control of our code base and specific issue-tracking.

#### 3.2 TASK DECOMPOSITION

Our project is split up into the following tasks, which will generally be completed in sequential order:

- 1. Tool Setup

- a. Install and set-up open-source software and example Caravel project

- b. Run RTL simulations, harden, and run GL simulations on the example Caravel project

- c. Successfully create, simulate, and harden custom components using the tool flow

- 2. Design Decomposition

- a. Determine how user projects interact with Management SoC, Wishbone bus, OpenRAM

- b. Define interconnections between components and necessary control paths

- c. Harden example user projects with different configurations to understand constraints

- d. Draw out a high-level framework schematic with all subcomponents, ports, and connections

- 3. Create Modules

- a. Implement each module in Verilog

- b. Create a testbench that thoroughly covers the module's functionality

- c. Successfully simulate and harden each component on its own

- 4. Integrate Modules

- a. Review modules and test benches written by each team member

- b. Place modules in the high-level project wrapper based on the design decomposition

- c. Configure and harden the project wrapper with all components added

- 5. Test Overall Design

- a. Place different user projects in the framework and test that each project can function

- b. Create and run tests that ensure the framework can properly connect and activate projects

- c. Create and run tests that ensure the framework meets timing, size, and power constraints

- d. Run project through pre-check and ensure all tests pass to prepare for fabrication

- 6. Submit Design to Efabless

- a. Create a repository and project on Efabless's website

- b. Submit our design to the Efabless Open MPW program by the intended deadline

- 7. Bring-Up Documentation & Physical Testing

- a. Thoroughly document our project's design, implementation, testing, and general use

- b. Create a detailed bring-up plan for the ISU Chip Fabrication team

- c. Run pre-fabrication physical tests on the ISU Chip Fabrication FPGA board

#### 3.3 PROJECT PROPOSED MILESTONES, METRICS, AND EVALUATION CRITERIA

Our project's milestones can be broken into the main task sections listed above. Each milestone will be measured using the following metrics:

- Milestone 1: Complete Tool Setup

- Each member can go through the RTL simulation, hardening, and GL simulation process on the example project.

- Each member will be able to view correctly simulated waveforms in GTKWave.

- Each member can successfully implement a new Verilog module and complete the same steps.

- Milestone 2: Complete Design Decomposition

- Framework will fully connect each user project to the Wishbone, LA, and IO ports

- Hardening configuration results will outline the necessary size and layout of user projects

- The framework schematic will illustrate the full interconnections between the user projects and management wrapper

- Milestone 3: Create All Modules

- Each implemented Verilog module will properly synthesize and function as expected

- $\circ$   $\:$  Each module's test bench will include base cases and edge cases for the design under test

- Each module will pass simulation and can be hardened on its own

- Milestone 4: Integrate All Modules

- All modules will fit into the user project wrapper in synthesis

- Each project will be fully connected to the Management SoC

- $\circ$   $\;$  The project wrapper successfully synthesizes and hardens after all components are added

- Milestone 5: Test Overall Design

- The project's resources will be multiplexed to the active project as selected in the software

- The project will meet all timing, size, and power constraints set by Caravel for the fabrication

- The project will successfully harden and pass all pre-check steps

- Milestone 6: Submit Design to Efabless

- The project will be placed in a public repository on Efabless

- The project will be fully submitted by the Efabless Fall 2024 deadline

- Milestone 7: Complete Bring-Up Documentation & Physical Testing

- Project documentation will be easy to understand and navigate without troubleshooting

- The bring-up plan will cover future testing and use cases for the ISU Chip Fabrication team

- The physical chip will fully support different user projects

| Task                           | Status      | Jan | Feb | March | April | May | <br>Aug | Sept | Oct | Nov | Dec |

|--------------------------------|-------------|-----|-----|-------|-------|-----|---------|------|-----|-----|-----|

| Project Setup                  | Done        |     |     |       |       |     |         |      |     |     |     |

| Setup tools and workspace      | Done        |     |     |       |       |     |         |      |     |     |     |

| Example project tutorials      | Done        |     |     |       |       |     |         |      |     |     |     |

| Design Decomposition           | Done        |     |     |       |       |     |         |      |     |     |     |

| Research components            | Done        |     |     |       |       |     |         |      |     |     |     |

| Draw schematic                 | Done        |     |     |       |       |     |         |      |     |     |     |

| Create Modules                 | In Progress |     |     |       |       |     |         |      |     |     |     |

| Implement modules              | In Progress |     |     |       |       |     |         |      |     |     |     |

| Test and harden each module    | In Progress |     |     |       |       |     |         |      |     |     |     |

| Integrate Modules              |             |     |     |       |       |     |         |      |     |     |     |

| Add modules to project wrapper |             |     |     |       |       |     |         |      |     |     |     |

| Implement interconnections     |             |     |     |       |       |     |         |      |     |     |     |

| Test Overall Design            |             |     |     |       |       |     |         |      |     |     |     |

| Test interconnections          |             |     |     |       |       |     |         |      |     |     |     |

| Test user projects             |             |     |     |       |       |     |         |      |     |     |     |

| Submit Design to Efabless      |             |     |     |       |       |     |         |      |     |     |     |

| Bring-Up and Physical Testing  |             |     |     |       |       |     |         |      |     |     |     |

| Test on firmware               |             |     |     |       |       |     |         |      |     |     |     |

| Create bring-up plan           |             |     |     |       |       |     |         |      |     |     |     |

#### 3.4 PROJECT TIMELINE/SCHEDULE

#### Figure 1: Project Timeline

The Gantt chart illustrates our projected timeline for this project, from start to finish. The timeline takes place over the Spring 2024 and Fall 2024 semesters and is broken down into individual weeks. Each major milestone is highlighted in a different color, and the milestone's expected deliverable deadline is at the end of the highlighted timeframe

#### 3.5 RISKS AND RISK MANAGEMENT/MITIGATION

We have identified the following major risks and appropriate mitigations of our project:

- Risk 1: Design does not pass pre-check

- Estimated Probability: 15%

- Mitigation: Use simulation tools to extensively check our design against the fabrication specifications. Run DRC and LVS checks to ensure our layout meets all rules and matches the expected schematic. Hold design reviews with our advisor and mentors who may catch potential issues early.

- Risk 2: OpenRAM modules cannot be hardened or fabricated in the framework

- Estimated Probability 10%

- Mitigation: Exclude OpenRAM modules from the framework design or leave space for OpenRAM modules to be added in the future. Until implemented, the user projects cannot utilize OpenRAM modules.

- Risk 3: Project wrapper area cannot fit framework and expected projects

- Estimated Probability: 10%

- Mitigation: Reduce the number of user projects the framework will support. The framework logic itself will likely not be able to be reduced due to wire spacing requirements.

- Risk 4: Error occurs during fabrication process or delivery

- Estimated Probability: 5%

- Mitigation: Include testing features in our design to test the fabrication process and ensure consistency in the physical chip. Plan for future redesigns or tweaks if the initial fabrication process fails.

| Task                                                                                           | Projected Hours |

|------------------------------------------------------------------------------------------------|-----------------|

| Tool Setup - installing tools, running example project                                         | 20              |

| Design Decomposition - researching components, drawing schematic                               | 20              |

| <b>Create Modules</b> - writing Verilog, simulating and hardening individual components        | 60              |

| Integrate Modules - integrating modules in top-level design, hardening wrapper                 | 40              |

| Test Overall Design - writing and running tests covering base and edge cases                   | 80              |

| <b>Submit Design to Efabless</b> - creating a public project repository, submitting the design | 10              |

| Bring-Up Documentation - documenting a detailed bring-up plan for                              | 80              |

#### 3.6 Personnel Effort Requirements

| future users                                                                              |    |

|-------------------------------------------------------------------------------------------|----|

| <b>Physical Testing</b> - receiving physical chip, running user projects in the framework | 40 |

Table 1: Effort Requirements

#### 3.7 Other Resource Requirements

Our design will be manufactured through the Efabless ChipIgnite program. Fabricating a single chip through this program costs \$9750, and the fabrication turnaround is about 4-5 months.

Our project also requires the following open-source resources and software:

- SkyWater 130nm Open-Source Process Design Kit (PDK)

- GTKWave

- KLayout

These tools are all free to use.

### 4 Design

#### 4.1 DESIGN CONTEXT

#### 4.1.1 Broader Context

Our project addresses the lack of ASIC development opportunities for undergraduate students. By creating our framework, we can provide a cost-effective solution to allow multiple student projects to be fabricated simultaneously. This ultimately supports a continuous cycle of chip prototypes, created by students at any experience-level.

| Area                                  | Description                                                                                                                                                                                                                                                  | Examples                                                                                                                                                                                                                           |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public health,<br>safety, and welfare | Our project provides practical<br>experience and skills development for<br>students, which is essential for<br>building a knowledgeable workforce<br>capable of addressing future public<br>health and safety challenges through<br>innovative technologies. | Students can gain experience in<br>chip fabrication and create designs<br>with any functionality. They can<br>gain experience and supplement<br>their education with a low barrier<br>to entry.                                    |

| Global, cultural,<br>and social       | By enabling students to design and<br>fabricate chips, our project<br>contributes to the accessibility of<br>technology development, by lowering<br>barriers for chip design and<br>fabrication.                                                             | The project could lead to initiatives<br>that focus on creating affordable<br>and accessible technology solutions<br>for underrepresented communities<br>or developing regions, fostering<br>greater social and digital inclusion. |

| Environmental | Our project involves the design of a<br>framework that allows multiple<br>projects to run independently but<br>share the same resources. This<br>approach can lead to more efficient<br>use of materials and energy,<br>highlighting the importance of<br>sustainable practices in engineering. | By creating reusable components,<br>the project can contribute to<br>reducing waste from excessive<br>fabrication, promoting an efficient<br>cycle of chip fabrication. |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Economic      | Our project allows multiple student<br>projects to be fabricated at once,<br>minimizing the cost of prototyping<br>multiple designs. It also contributes<br>to students' learning and<br>development of valuable skills, which<br>will be beneficial in the workforce.                          | The use of open-source work allows<br>users to create their own ASIC<br>designs at minimal cost.                                                                        |

Table 2: Project Context

#### 4.1.2 Market Research

After investigating existing solutions for entry-level ASIC fabrication, we found that the company Tiny Tapeout is the other main competitor to Efabless. However, we found several factors about Tiny Tapeout's fabrication program that make their solution unsuitable for our project.

Tiny Tapeout's chip space is 160um x 100um, which allows for 1000 digital logic gates. This user space is extensively smaller than Efabless's, and it would not provide enough space to include the desired number of projects and interfaces that our framework will implement. Due to its limited size and interfaces, the Tiny Tapeout chip also has limited testing capabilities compared to Efabless. For these reasons, our design will use the Efabless process.

Additionally, we will be building upon the work of prior senior design teams who have developed various ASIC projects. We have access to their designs and the documentation detailing their development process. However, our project is unique because it is implementing a framework that can support multiple projects like the ones created by the senior design teams.

Prior Senior Design Teams:

- http://sdmay23-28.sd.ece.iastate.edu

- http://sddec23-08.sd.ece.iastate.edu

- https://sddec23-o6.sd.ece.iastate.edu

#### 4.1.3 Technical Complexity

Our design has multiple components and interfaces that contribute to its complexity:

- Wishbone Interface

- We need to implement the Wishbone bus interface between the Management SoC and the user projects. This communication protocol allows data to be transmitted between the management and user area, and it will be used to send various control

values to configure the framework. We must implement a way to read and store the control values through the Wishbone interface, while also allowing the user projects to use the interface to access the Management SoC memory.

- External OpenRAM

- In addition to the memory provided by the Management SoC, we are including additional, independent memory modules in our design. This allows projects to use external memory. We must incorporate the pre-hardened, 8-bit OpenRAM modules into our design to allow projects to read and write 32-bit data. To do this, we must create a Wishbone interface between the OpenRAM modules and the user projects.

- Support of Different User Projects

- Multiple user projects need to be able to interface with the Management SoC utilities and other chip resources. Only the single active project can send and receive data at a time. The inactive projects should be able to hold their state. The projects have independent reset signals. We are also looking into allowing the user projects to have varying frequencies, which would involve clock gating.

#### 4.2 DESIGN EXPLORATION

#### 4.2.1 Design Decisions

There were several design decisions that we had to make when planning out our framework design. Beyond the basic functionality requirements, our client allowed us to decide on the following:

- 1. How many projects that our framework will support

- The total number of user projects will affect how resources are multiplexed. It also limits how big each user project can be, as we have limited space within the design area.

- 2. How different user projects will be activated

- Our design should only allow one project to be "active" at a time. The active project will be reading and writing output data and utilizing memory. We must figure out how to enable and disable all the projects independently within the framework.

- 3. How projects will interface with the management core

- Each project should be connected to all the chip's resources and, when active, be able to read and write data from the management core. We must design an interface that allows all the projects to communicate independently with the management core.

- 4. How to incorporate OpenRAM with the user projects

- OpenRAM is a memory module that is independent of the memory in the management core. It provides external memory to the user projects. We must decide how to connect existing OpenRAM modules to the user projects and how many of the OpenRAM modules to include in the overall design.

#### 4.2.2 Ideation

We based our design decisions on example projects and suggestions from our client:

- 1. We decided to implement 15 small projects and 2 large projects. These numbers were based on the size of completed, for example, user projects. This choice may change if we run into sizing constraint issues.

- 2. The active user project will be selected through the management core. A select value will be written to a dedicated address in memory through software. Another option was to use physical dip switches, but we implemented project control in software for simplicity.

- 3. We decided to multiplex all the chip's resources to the different projects based on the select value mentioned before. This method is widely used in digital design. Our interconnection design is explained in more detail in the following sections.

- 4. We decided to include four 8-bit OpenRAM modules in our design. This way, 32-bit data can be written and read across the four modules. However, incorporating OpenRAM in our design requires additional ports to be added to each user project. This results in a bigger project size. For this reason, we thought of several possible solutions to minimize the size increase:

- Add the necessary set of OpenRAM ports to every project

- Utilize existing IO pins for OpenRAM interfacing

- Chain the OpenRAM modules in a sequential fashion, instead of in parallel

- Interface with the OpenRAM modules through the Wishbone protocol

#### 4.2.3 Decision-Making and Trade-Off

To decide which method to use for OpenRAM integration, we considered the following trade-offs:

- Add the necessary set of OpenRAM ports to every project

- **Pros:** Simplest option; does not require additional logic besides multiplexing

- **Cons:** Results in a lot of additional ports per project; since we have 4 separate OpenRAM modules, each project will need an additional (4 \* # OpenRAM ports)

- Utilize existing IO pins for OpenRAM interfacing

- **Pros:** Does not require any additional ports to be added

- **Cons:** Limits a project's use of IO ports; requires control module to identify which and when IO ports will be used for memory

- Chain the OpenRAM modules in a sequential fashion, instead of in parallel

- **Pros:** Reduces number of additional ports to just (1 \* # OpenRAM ports)

- **Cons:** Increases number of cycles needed for deeper memory accesses, since each module uses 1 clock cycle; requires control module to appropriately mask address bits between the different modules

- Interface with the OpenRAM modules through the Wishbone protocol

- **Pros:** Projects will have 1 additional set of Wishbone Master ports; no additional ports for interacting directly with OpenRAM modules

- **Cons:** Requires an OpenRAM wrapper that maps its ports to Wishbone Slave ports; does not support parallel memory accesses

Based on these comparisons, we decided to go with the last method: using the Wishbone protocol. We chose this option because it should be straightforward to implement and has the least significant drawbacks in size, functionality, and performance.

#### 4.3 PROPOSED DESIGN

#### 4.3.1 Overview

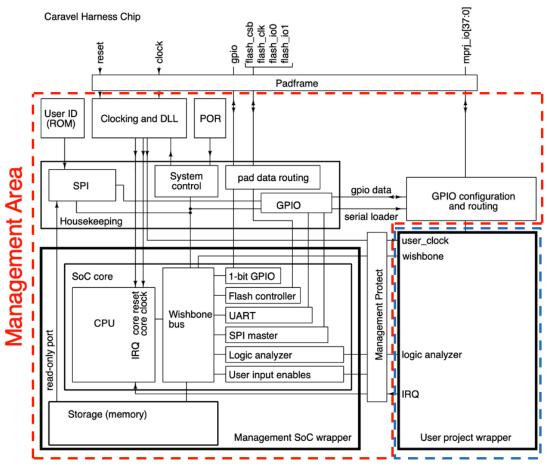

Our design uses the open-source Caravel user project template, which can be found on GitHub. This project template is designed specifically for the chip fabrication program we are using. The Caravel chip architecture is shown below in Figure 3.

Figure 2: Caravel Chip Architecture [1]

The user project wrapper, outlined in blue in the lower right corner, is the chip's user area. This is where our framework and all user project modules will be implemented. The part outlined in red is the management core. This space contains the chip's resources, including memory, the Wishbone Master, the logic analyzer, and GPIO configuration. The management core is configured externally through software. Our framework will connect the various management core ports to the user projects, as shown in Figure 3.

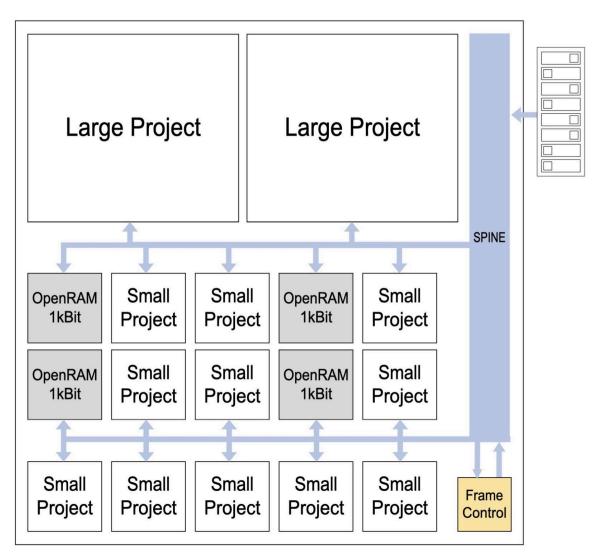

Figure 3: Framework Diagram

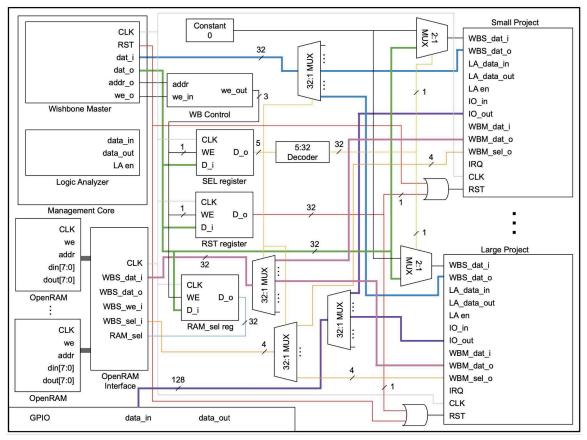

#### 4.3.2 Detailed Design and Visual(s)

Figure 4 depicts the general design composition of our user project framework. Our design connects small, interchangeable user projects, pictured on the right, to the resources provided by the Management Core SoC, pictured on the left, and the GPIO ports. Only one user project will be active and communicating with the Managemen SoC at a time. The Management SoC contains the Wishbone Bus (WB) Master and the Logic Analyzer (LA) modules. Both of these are used to communicate with the user projects and transfer data, and there are separate ports for data going in and out of these modules.

Each project can be reset individually. The project reset bus signal will come from the Wishbone Bus and be stored in the RST register. The active user project will be selected using a value outputted by the Wishbone Bus and stored in the SEL register. Each project's data output will be multiplexed based on the selected value and returned to the Management SoC. The data sent from the Management SoC to the small projects will be inputted to the active small project. Inactive projects will receive data that is all zeros. 2-1 multiplexers will select between the resource data and o values, and the select bits will come from a one-hot decoder.

Figure 4: Design Schematic

Acronyms

- CLK: Clock; system clock used by the Management SoC and all projects

- **GPIO:** General-Purpose Input/Output; ports handling both incoming and outgoing digital signals

- IO: Input/Output; data transfer to or from the chip

- **IRQ:** Interrupt Request Signal; designates peripheral devices/processes that are ready within a module to be serviced by the Management SoC

- LA: Logic Analyzer; sends logic signals between the Management SoC and user projects

- **RST:** Reset; when high, clears all module values to o

- **SoC:** System-on-a-chip, integrated circuit design that combines the functions of an electronic device onto a single chip

- WB: Wishbone Bus; connects modules to the Management SoC and handles data transfers

- **WBS:** Wishbone Bus Slave; module that responds to transactions initiated by the Wishbone Bus master in the Management SoC

- WE: Write enable; signal that enables writing data to the respective location

#### 4.3.3 Functionality

With our design, users will be able to create independent ASIC projects and place them as macros in our framework. As we stated before, multiple projects can be placed in the framework at once, and each project will be able to run independently and access the management core.

After placing their project in our framework, the user will configure the management core through software to select their project as active. They will then be able to interact with their project normally, with the same functionality as if their project was the only component inside the user space.

#### 4.3.4 Areas of Concern and Development

Throughout our brainstorming and design process, we have had regular communication with our client to ensure our design will meet user needs. However, due to the nature of the project, we have two main concerns:

- Will our solution's current level of complexity support all possible projects going forward?

- With our solution's current level of complexity, will all expected modules fit in the die area?

We have communicated these concerns with our client, and they have expressed that the total number of projects can be reduced if needed. They have also approved of our design, so we can assume that future user projects will be appropriately supported within reason.

Additionally, our client outlined stretch goals to strive for once we get further in the development process:

- Optimize power through clock gating on inactive projects

- Preserve the state of all inactive projects, rather than resetting them in between uses

#### 4.4 TECHNOLOGY CONSIDERATIONS

Our project fully utilizes open-source tools and project architecture. Open-source software is usually free to use and modify, making it a cost-effective solution. Our project architecture is accessible to anyone and publicly published on GitHub. Open-source projects also often have a large community of contributors that can help find and fix bugs.

However, there are also trade-offs. Open-source projects often lack official support or documentation, resulting in a learning curve for new users. Throughout our planning and design process, we have sometimes needed to search through multiple repositories and wiki pages to find the data we are looking for. Additionally, open-source software can have compatibility issues, as projects may not always have full integration with different operating systems. To combat this, we are using a Linux virtual machine that contains an installed toolflow as our development environment. This way, our team does not have to worry about environmental inconsistencies or incompatibilities.

#### 4.5 DESIGN ANALYSIS

| Component  | Run # | Changed Settings      | # Ports | CLOCK_PERIOD | CLOCK_PORT | CLOCK_NET | FP_SIZING | DIE_AREA    | PL_TARGET_DENSITY | Pass? (Y/N) | Errors                                     | Notes                                                                                               | Date Run |

|------------|-------|-----------------------|---------|--------------|------------|-----------|-----------|-------------|-------------------|-------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------|----------|

| adder_wrap | 1     | ~                     | 607     | 25 (40 MHz)  | wb_clk_i   | [blank]   | absolute  | 0 0 700 700 | 0.55              | Y           |                                            |                                                                                                     | 4/2/24   |

| adder_wrap | 2     | DIE_AREA              | 607     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 350 350 | 0.55              | N           | Failed on step 4<br>(Running IO placement) | [ERROR PPL-0024] Number of IO pins<br>(607) exceeds maximum number of<br>available positions (424). | 4/2/24   |

| adder_wrap | 3     | DIE_AREA              | 607     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 525 525 | 0.55              | Y           |                                            |                                                                                                     |          |

| adder_wrap | 4     | DIE_AREA              | 607     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 438 438 | 0.55              | N           | Failed on step 4<br>(Running IO placement) | [ERROR PPL-0024] Number of IO pins<br>(607) exceeds maximum number of<br>available positions (530). | 4/2/24   |

| adder_wrap | 5     | DIE_AREA              | 607     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 482 482 | 0.55              | N           | Failed on step 4<br>(Running IO placement) | [ERROR PPL-0024] Number of IO pins<br>(607) exceeds maximum number of<br>available positions (584). | 4/2/24   |

| adder_wrap | 6     | DIE_AREA              | 607     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 500 500 | 0.55              | N           | Failed on step 4<br>(Running IO placement) | [ERROR PPL-0024] Number of IO pins<br>(607) exceeds maximum number of<br>available positions (606). | 4/2/24   |

| adder_wrap | 7     | DIE_AREA              | 607     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 501 501 | 0.55              | Y           |                                            |                                                                                                     | 4/2/24   |

| adder_wrap | 8     | PL_TARGET_DENSITY     | 607     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 501 501 | 1                 | Y           |                                            |                                                                                                     | 4/2/24   |

| adder_wrap | 9     | Added WB master ports | 711     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 700 700 | 0.55              | Y           |                                            |                                                                                                     | 4/9/24   |

| adder_wrap | 10    | DIE_AREA              | 711     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 501 501 | 0.55              | N           | Failed on step 4<br>(Running IO placement) | [ERROR PPL-0024] Number of IO pins<br>(711) exceeds maximum number of<br>available positions (608). | 4/9/24   |

| adder_wrap | 11    | DIE_AREA              | 711     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 550 550 | 0.55              | N           | Failed on step 4<br>(Running IO placement) | [ERROR PPL-0024] Number of IO pins<br>(711) exceeds maximum number of<br>available positions (666). | 4/9/24   |

| adder_wrap | 12    | DIE_AREA              | 711     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 575 575 | 0.55              | N           | Failed on step 4<br>(Running IO placement) | [ERROR PPL-0024] Number of IO pins<br>(711) exceeds maximum number of<br>available positions (696). | 4/9/24   |

| adder_wrap | 13    | DIE_AREA              | 711     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 600 600 | 0.55              | Y           |                                            |                                                                                                     | 4/9/24   |

| adder_wrap | 14    | DIE_AREA              | 711     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 585 585 | 0.55              | N           | Failed on step 4<br>(Running IO placement) | [ERROR PPL-0024] Number of IO pins<br>(711) exceeds maximum number of<br>available positions (708). | 4/9/24   |

| adder_wrap | 15    | DIE_AREA              | 711     | 25           | wb_clk_i   | [blank]   | absolute  | 0 0 586 586 | 0.55              | N           | Failed on step 4<br>(Running IO placement) | [ERROR PPL-0024] Number of IO pins<br>(711) exceeds maximum number of<br>available positions (710). | 4/9/24   |

| adder wrap | 16    | DIE AREA              | 711     | 25           | wb clk i   | [blank]   | absolute  | 0 0 587 587 | 0.55              | Y           |                                            |                                                                                                     | 4/9/24   |

#### Figure 5: Hardening Data

Our team has researched and become familiar with the Caravel project architecture. We have begun implementing and testing the various low-level components our design uses, including a variable size register, a 2-to-1 multiplexer, and a 5-to-32 decoder. As we verify these designs through simulations, we can begin implementing the base design we outlined earlier.

One important step of the build process is hardening designs, which consists of synthesis, place and route, and error checking. Successful hardening results in generated GDSII files. While a component may pass simulation, it must also be hardened to ensure the design will work once implemented on hardware. In order to harden a design, a configuration file must be created that contains settings for various parameters, such as design size, clock frequency, and density. Part of the design process involves finding the optimal configuration settings that allow hardening to pass, while still meeting project constraints.

In order to find the best configuration, we have run various hardening configurations on an example project and recorded the results, as shown in Figure 5. As we experiment with different parameter values, we can determine the various constraints we will need to consider when implementing the wrapper for the different user projects. Based on the data we have collected so far, we have found that a project area can have a minimum size of  $501 \,\mu\text{m} \times 501 \,\mu\text{m}$  while still supporting the expected  $607 \,\text{ports}$ . We plan to also test different clock periods to see what frequencies can still meet all timing tests.

### 5 Testing

We have a comprehensive testing plan that will thoroughly test all of our submodules and the top-level framework design. We want to ensure every component in our design is fully functional and passes hardening and pre-check in preparation for fabrication.

#### 5.1 UNIT TESTING

All of the modules in our design will have one test that covers basic use and edge cases of their functionality. These tests will be written as Verilog testbenches. They will be performed by RTL and

GL simulations with the OpenROAD tools. We will use GTKWave to view and verify the test results. We will test each component as they are implemented.

Modules Under Test:

- 5 to 32 Decoder

- 32 to 1 Multiplexer

- N-bit Register

- Wishbone Bus Control Module

- OpenRAM Module

- Example User Projects

We have already begun unit testing. Results can be seen in Appendix 10.1.

#### 5.2 INTERFACE TESTING

We will also test interfaces between components to ensure communication between the various components of our framework. These tests will verify writing and reading values between the master and slave modules, as well as ensure that modules adhere to the bus protocols. These tests will be written as Verilog testbenches. They will be performed by RTL and GL simulations with the OpenROAD tools. We will use GTKWave to view and verify the test results.

Interfaces Under Test:

- Wishbone Bus Interface with User Projects

- GPIO Interface with User Projects

- LA Interface with User Projects

- OpenRAM Wishbone Bus Interface with User Projects

#### 5.3 INTEGRATION TESTING

After testing individual modules and interfaces, we will integrate everything into the top-level user project wrapper to create our framework design. We will ensure that all connections are implemented according to our design schematic. From there, we will undergo extensive testing of our overall framework, utilizing example user projects to place in our design. We will create tests that verify different projects can be enabled, and that all user projects can properly access the chip resources when active.

#### 5.4 System Testing

Upon integration, we will test our framework by creating multiple testbenches that implement and activate different example user projects. We will simulate C code to program the Management SoC to verify that the user projects can properly interface with the various chip utilities. We will also run the user project wrapper through hardening and pre-check to ensure the design can be properly synthesized. This will involve creating hardening configurations that properly set different hardening parameters for the project.

#### 5.5 REGRESSION TESTING

To ensure we are not creating errors and breaking our existing "functional" product, we will incrementally insert pieces of our project together and run the same tests or slightly edited versions to check our results. Assuming everything operates as we intend, we will see the same results and individual stages throughout this testing. The two main stages to test our projects with and without

the OpenRAM modules. Without memory should prove to be much easier, and once we have that as a base for testing we can insert multiple memoryless projects to ensure we can operate more than one project in our project. Finally, we would complete the same process with memory projects and a combination of both.

#### 5.6 ACCEPTANCE TESTING

Once we have ensured our design meets all functionality requirements, we will harden our design through the OpenROAD toolflow to ensure we meet timing and area requirements. This process includes place and route and finding the optimal hardening configuration. We will then verify our design meets all fabrication specifications by running Efabless precheck on our project. Precheck will perform additional DRC and LVS tests.

#### 5.7 BRING-UP & PHYSICAL TESTING

After passing acceptance testing and submitting our design to Efabless, we will develop a bring-up testing plan. This will include a test project template that future users will use to test that their project can be integrated into our framework. The template will include the OpenRAM modules and interface, as well as the expected connections with the rest of the chip. Users will utilize the template to ensure their design successfully interfaces with all components of our framework before integrating their project into our design.

We will also utilize the ISU Chip Fabrication FPGA board for physical tests. Our design will be flashed to the FPGA board, so we can perform physical testing before our chip finishes fabrication.

#### 5.8 RESULTS

Our testing results will be waveforms collected from running test benches on our components. Because we are creating the test benches, we will have expected output values when looking at the waveforms. We can tell if we meet the speed and data requirements needed to call our tests successful through these graphs. Additionally, successful acceptance testing will produce successful hardening and precheck logs that demonstrate our design meets all required checks.

# 6 Implementation

Our implementation plan for next semester will cover Milestones 4-7:

- Milestone 4: Integrate All Modules

- Milestone 5: Test Overall Design

- Milestone 6: Submit Design to Efabless

- Milestone 7: Complete Bring-Up Documentation & Physical Testing

Currently, we have already begun implementing basic modules and performing unit tests. We plan to finish individual module implementation and begin integrating everything into the top-level wrapper shortly after next semester begins. Testing will take place throughout implementation until the Efabless submission deadline, in late October or early November. After submission, we will focus on developing our bring-up and physical testing plan.

# 7 Professional Responsibility

### 7.1 Areas of Responsibility

| Responsibilities              | Our Definition                                                                                               | IEEE Definition                                                                               | NSPE Definition                                                                                                                                                |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Work Competence               | Performing work that<br>is your own and meets<br>the standards you have<br>set.                              | Perform work of high<br>quality, integrity,<br>timeliness, and<br>professional<br>competence. | Perform services only<br>in areas of their<br>competence; Avoid<br>deceptive acts                                                                              |  |

| Financial<br>Responsibility   | The product we deliver<br>will be created using<br>reliable components<br>and with reliable<br>services.     | Deliver products and<br>services of realizable<br>value and at reasonable<br>costs            | Act for each employer<br>or client as faithful<br>agents or trustees                                                                                           |  |

| Communication<br>Honesty      | We will communicate<br>and collaborate to<br>provide the best<br>product possible.                           | Report work truthfully,<br>without deception, and<br>understandable to<br>stakeholders.       | Issue public statements<br>only in an objective<br>and truthful manner;<br>Avoid deceptive acts                                                                |  |

| Health, Safety,<br>Well-Being | We will practice safe<br>procedures and not<br>cut corners to create<br>hazards to the users or<br>ourselves | Minimize risks to the<br>safety, health, and<br>well-being of<br>stakeholders.                | Hold paramount the<br>safety, health, and<br>welfare of the public                                                                                             |  |

| Property<br>Ownership         | We will not steal the<br>ideas or take<br>responsibility for<br>products that are not<br>ours.               | Respect the property,<br>ideas, and information<br>of clients and others.                     | Act for each employer<br>or client as faithful<br>agents or trustees.                                                                                          |  |

| Sustainability                | We will create a<br>product that meets<br>our standards and will<br>withstand constant<br>use.               | Protect the<br>environment and<br>natural resources locally<br>and globally.                  | N/A                                                                                                                                                            |  |

| Social<br>Responsibility      | Our product will<br>better advance the<br>users.                                                             | Produce products and<br>services that benefit<br>society and<br>communities.                  | Conduct themselves<br>honorably, responsibly,<br>ethically, and lawfully<br>so as to enhance the<br>honor, reputation, and<br>usefulness of the<br>profession. |  |

#### Table 3: Areas of Responsibility

#### 7.2 PROJECT SPECIFIC PROFESSIONAL RESPONSIBILITY AREAS

| Responsibilities              | Relation to Our Project                                                                                     | Performance                                                                                                                                                    |

|-------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Work Competence               | We should hold ourselves to use our work and not steal from others.                                         | We have been creating and using<br>our work and ideas within our<br>project.                                                                                   |

| Financial<br>Responsibility   | We must be mindful of fabrication<br>costs by working to meet<br>submission deadlines.                      | We are working towards the Fall<br>2024 deadline.                                                                                                              |

| Communication<br>Honesty      | We must hold ourselves accountable<br>to communicate with each other<br>and our client.                     | We have been communicating<br>our progress to our client and<br>sharing ideas between team<br>members, but we could increase<br>communications and timeliness. |

| Health, Safety,<br>Well-Being | We should promote a supportive<br>learning environment for our future<br>users and for ourselves.           | We are considering our users and<br>the user experience throughout<br>the design process.                                                                      |

| Property Ownership            | We must respect the ideas of our clients and our teammates.                                                 | We have shared and respected<br>every team member's ideas and<br>work throughout the project.                                                                  |

| Sustainability                | We should adopt energy-efficient<br>design practices and choose<br>sustainable materials for<br>components. | We have make various design<br>decisions based on performance<br>trade-offs.                                                                                   |

| Social Responsibility         | We are responsible for providing a product to enhance users' learning.                                      | We have kept the goal of our<br>product which is to enhance the<br>learning capabilities of the user<br>in mind while completing our<br>project.               |

#### 7.3 MOST APPLICABLE PROFESSIONAL RESPONSIBILITY AREA

Our most applicable professional responsibility area is Social Responsibility.

Our team has a social responsibility to provide the best product we can to the student users to facilitate learning for future students. We plan to consider every type of user and how they might think differently. We will use these ideas to create an easy-to-use solution that allows them to learn more about ASIC development. We will also have thorough testing to ensure our product meets our standards. This approach will cover more than just our social responsibility to provide a product that facilitates the learning experience. It can also make it fun both for the users and us.

# 8 Closing Material

#### 8.1 DISCUSSION

Our group began by learning to use tools and equipment provided by our client and previous groups. This consisted of tests and examples by Caravel Efabless. After becoming familiar with the tools we began to experiment and create our files and run our tests. This was the start of our framework, and most of our work is related to this process. We have created a schematic for our design.. This has been the base for our components work including register files, decoders, and muxes.

Our biggest challenges were learning the tools and learning the Verilog coding language. These challenges did not stop us as previous groups have provided documentation on the tools, and the internet provides multiple examples of Verilog. Our next step is to determine the memory aspect of our project. There is not a lot of documentation on this, and it is up to our team to experiment and run tests to determine the best way to implement it.

In the future, we will have to run tests on the completed framework to ensure that our project behaves the way it was designed. We will have to place an order for our design to be created and chips to be sent to Iowa State.

#### 8.2 CONCLUSION

Our project is to build a chip framework that supports user ASIC projects created by students in the ISU Chip Fabrication Co-Curricular Team. For our design, we are using open-source tools and project architecture provided by Efabless. The chip framework will integrate the modules into a unified ASIC by connecting each module to the chip's GPIOs and management wrapper, or microcontroller. All of the chip's resources will be multiplexed between the different projects, depending on which is active at the time. The design process will involve creating a chip layout and fully functional management core, as well as configuration scripting, Verilog coding, and C programming. Through hardening tests and component simulations, we will ensure that our design is functional and can be properly fabricated. During the second semester of senior design, we will focus on implementing our design and running thorough tests to verify functionality. We will also develop a detailed bring-up plan for future students that will use our framework.

#### 8.3 REFERENCES

#### **Technical References:**

"Caravel Harness," *Efabless*. [Online]. Available: https://caravel-harness.readthedocs.io/en/latest/. [Accessed April 16, 2024].

"Caravel Management SoC," *Efabless*. [Online]. Available: https://caravel-mgmt-soc-litex.readthedocs.io/en/latest/. [Accessed April 16, 2024].

Efabless, "Efabless/caravel\_user\_project," *GitHub*. [Online]. Available: https://github.com/efabless/caravel\_user\_project. [Accessed April 16, 2024].

"Tiny Tapeout," *Tiny Tapeout*. [Online]. Available: https://tinytapeout.com/. [Accessed April 30, 2024].

#### Figures:

[1] Efabless, "Efabless/caravel," *GitHub*. [Online]. Available: https://github.com/efabless/caravel. [Accessed April 16, 2024].

# 9 Team

#### 9.1 TEAM MEMBERS

- Mitchell Driscoll

- Evan Dunn

- Baoshan Liang

- Katie Wolf

#### 9.2 Skill Sets Covered by the Team

- Mitchell Circuit board design, code debugging

- Evan Verilog development

- Baoshan Verilog code debugging

- Katie System design, Verilog development

#### 9.3 PROJECT MANAGEMENT STYLE ADOPTED BY THE TEAM

Combination of Waterfall and Agile

#### 9.4 INITIAL PROJECT MANAGEMENT ROLES

- Mitchell Component Implementation

- Evan Researcher, Design Testing

- Baoshan Design Testing

- Katie System and Component Design

#### 9.5 TEAM CONTRACT

#### Team Members:

#### 3) Boashan Liang 4) Katie Wolf

#### **Team Procedures**

- 1. Day, time, and location (face-to-face or virtual) for regular team meetings:

- Tuesday 4-5 pm with Dr. Duwe

- Thursday 2-3 pm with just team members

- $\circ$   $\;$  As needed digitally when something comes up.

- 2. Preferred method of communication updates, reminders, issues, and scheduling (e.g., e-mail, phone, app, face-to-face):

- Discord and Teams

- 3. Decision-making policy (e.g., consensus, majority vote):

- Consensus, with potential veto with cause.

- 4. Procedures for record keeping (i.e., who will keep meeting minutes, how will minutes be shared/archived):

- Use GitHub and Google Drive to take notes and share files

- Share links and resources through Discord

#### Participation Expectations

- 1. Expected individual attendance, punctuality, and participation at all team meetings:

- All members are present and on time for meetings

- Let others know ahead of time if you will be late or absent

- Exceptions permitted in regard to unexpected delays, sicknesses, etc

- 2. Expected level of responsibility for fulfilling team assignments, timelines, and deadlines:

- Meet deadlines as best as you can

- All members contribute to team assignments

- Submissions and contributions should be submitted in a timely manner unless otherwise excused via aforementioned exceptions.

- 3. Expected level of communication with other team members:

- Regular communication throughout the week

- Let others know immediately if issues or concerns come up

- Respond to messages within 24 hours

- 4. Expected level of commitment to team decisions and tasks:

- Commit to decisions decided as a team

- Voice concerns as soon as possible

- Each member should commit at least a significant portion of their time to the active development of the project.

#### Leadership

- 1. Leadership roles for each team member (e.g., team organization, client interaction, individual component design, testing, etc.):

- Evan team organization

- Mitchell schematic design

- Baoshan design testing

- Katie schematic and component design

- 2. Strategies for supporting and guiding the work of all team members:

- Gentle reminders, along with active guidance regarding development and subject matter. A clear statement of expectations when it comes to weekly and monthly progress.

- Excessively plan every facet of the project so that there are no surprises and everyone can fully commit.

- 3. Strategies for recognizing the contributions of all team members:

- Rigorously document individual and group accomplishments throughout the Semester.

- Clear documentation and acknowledgment of past accomplishments. Focus on the project as a whole. with support from others.

#### **Collaboration and Inclusion**

- 1. Describe the skills, expertise, and unique perspectives each team member brings to the team.

- Evan Computer Engineering Major, Digital design, "Industry contacts."

- Mitchell Electrical Engineering major, Schematic and PCB design

- Baoshan Electrical Engineering major, Schematic and layout, DRC and LVS check

- Katie Computer Engineering major, computer architecture, digital design

- 2. Strategies for encouraging and supporting contributions and ideas from all team members:

- Asking everyone for ideas

- Looking into all the ideas that are given

- Get everyone's feedback on each idea

- 3. Procedures for identifying and resolving collaboration or inclusion issues (e.g., how will a team member inform the team that the team environment obstructs their opportunity or ability to contribute?)

- $\circ$   $\;$  Be honest and communicate early on

- $\circ$  ~ Get the entire team's input on issues

#### Goal-Setting, Planning, and Execution

- 1. Team goals for this semester:

- Meet the client's expected deliverables given in the project documentation.

- Establish early on team expectations and finish ahead of deadlines to maximize testing.

- Establish a unified level of knowledge regarding the subject material.

- 2. Strategies for planning and assigning individual and teamwork:

- Assign tasks based on team members' expertise and availability

- Make sure all members have around the same amount of responsibility

- Use our suggested communication systems to inform the group when doing solo work.

- 3. Strategies for keeping on task:

- Meet regularly and review upcoming tasks and deadlines

- Check in on each other and hold each other accountable

• Request review by a peer or sponsor if any systemic or personal problems arise.

#### **Consequences for Not Adhering to Team Contract**

- 1. How will you handle infractions of any of the obligations of this team contract?

- Talk to the other team members

- Review the contract and expectations

- Involve higher authority when necessary.

- Mandatory disembowelment.

- 2. What will your team do if the infractions continue?

- Talk to Professor Shannon and Professor Fila

- Discuss further measures.

- Repeat the process of disembowelment just for good measure.

- a. I participated in formulating the standards, roles, and procedures as stated in this contract.

- b. I understand that I am obligated to abide by these terms and conditions.

- c. I understand that if I do not abide by these terms and conditions, I will suffer the consequences as stated in this contract.

| 1) Mitchell Driscoll | DATE: 1/30/24 |

|----------------------|---------------|

| 2) Evan Dunn         | DATE: 1/30/24 |

| 3) Baoshan Liang     | DATE: 1/30/24 |

| 4) Katie Wolf        | DATE: 1/30/24 |

# 10 Appendix

#### 10.1 SIMULATION WAVEFORMS

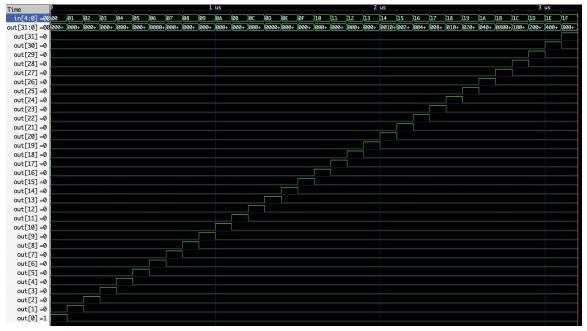

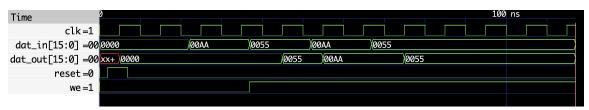

We have finished implementation and unit testing for the following modules:

- 32-to-1 decoder

- N-bit register

- Wishbone control module

The waveform results for these unit tests are shown in Figures 6-8.

Figure 6: 32-to-1 Decoder

Figure 7: N-Bit Register

Figure 8: Wishbone Control Module